工程师开发“高层”3D 芯片,实现更高效的 AI 硬件

作者:by Massachusetts Institute of Technology

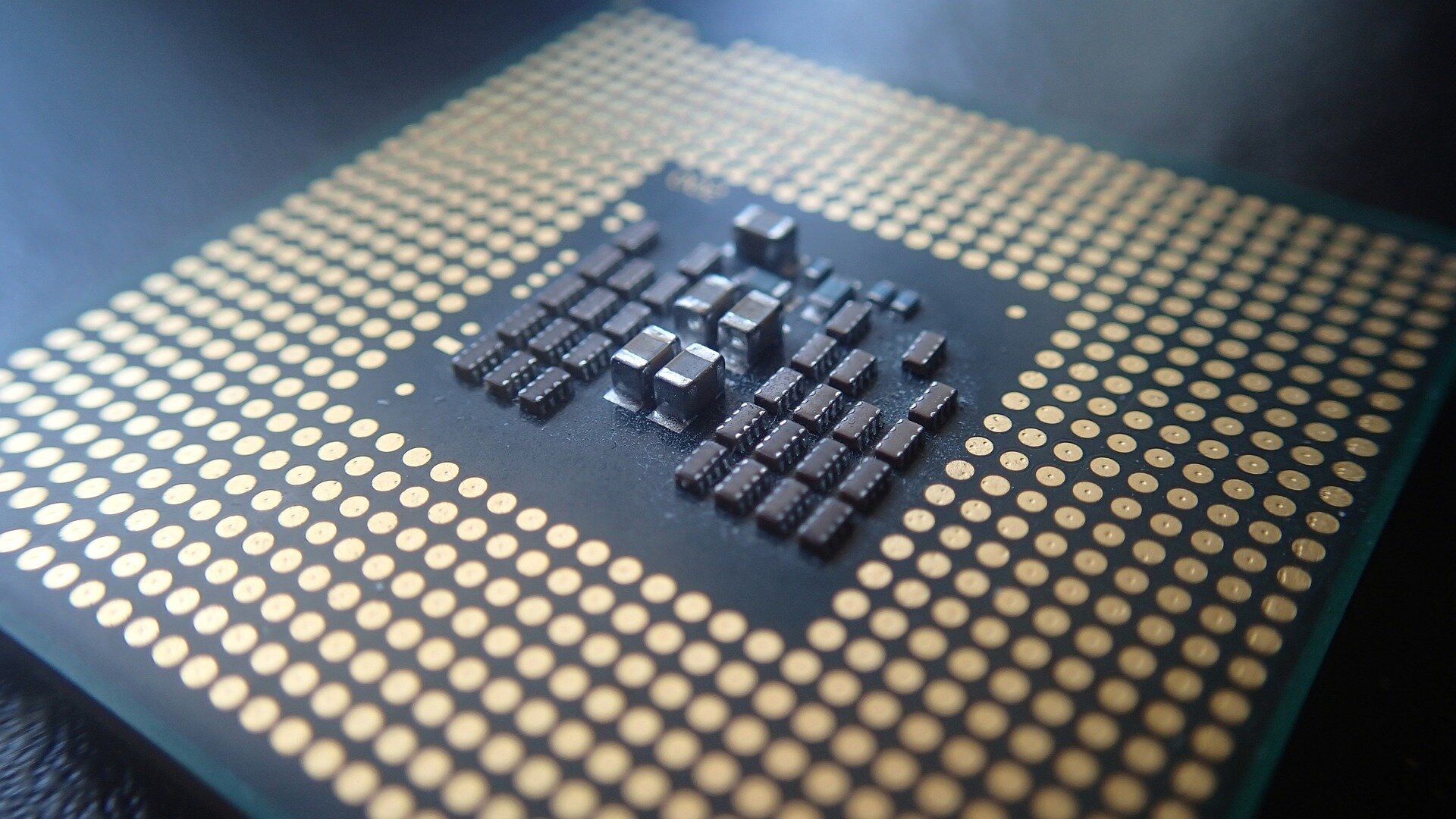

电子行业正在接近计算机芯片表面上可以封装的晶体管数量的极限。因此,芯片制造商正在寻求建立而不是淘汰。

该行业的目标不是将越来越小的晶体管挤压到单个表面上,而是堆叠晶体管和半导体元件的多个表面,类似于将牧场房屋变成高层建筑。与当今的电子产品相比,这种多层芯片可以处理更多的数据并执行更复杂的功能。

然而,一个重大障碍是构建芯片的平台。如今,大块硅片成为生长高质量单晶半导体元件的主要支架。任何可堆叠芯片都必须包含厚硅“地板”作为每一层的一部分,从而减慢功能半导体层之间的任何通信。

现在,麻省理工学院的工程师已经找到了解决这一障碍的方法,即采用多层芯片设计,不需要任何硅晶圆基板,并且可以在足够低的温度下工作以保护底层电路。

在一项研究中出现在日记中自然,该团队报告使用新方法制造多层芯片,该芯片具有直接在彼此顶部生长的交替层高质量半导体材料。

该方法使工程师能够在任何随机晶体表面上构建高性能晶体管以及存储器和逻辑元件,而不仅仅是在硅晶圆的庞大晶体支架上。研究人员表示,如果没有这些厚硅基板,多个半导体层可以更直接接触,从而实现层间更好、更快的通信和计算。

研究人员设想,该方法可用于构建人工智能硬件,以笔记本电脑或可穿戴设备的堆叠芯片的形式,其速度和功能与当今的超级计算机一样快,并且可以像物理数据中心一样存储大量数据。

“这一突破开启了巨大的潜力半导体产业研究作者、麻省理工学院机械工程副教授 Jeehwan Kim 表示:“这使得芯片的堆叠不受传统限制。这可能会导致人工智能、逻辑和内存应用的计算能力出现数量级的提高。”

该研究的麻省理工学院合著者包括第一作者 Ki Seok Kim、Seunghwan Seo、Doyoon Lee、Jung-El Ryu、Jekyung Kim、Jun Min Suh、June-chul Shin、Min-Kyu Song、Jin Feng 和 Sangho Lee,以及来自三星高级技术学院、韩国成均馆大学和德克萨斯大学达拉斯分校的合作者。

种子袋

2023年,金氏集团报道他们开发了一种在非晶表面生长高质量半导体材料的方法,类似于成品芯片上半导体电路的不同形貌。

他们生长的材料是一种被称为过渡金属二硫属化物(TMD)的二维材料,被认为是制造更小、高性能晶体管的硅的有前途的替代品。这种二维材料即使在小到一个尺寸的情况下也能保持其半导体特性单原子,而硅的性能急剧下降。

在之前的工作中,该团队在具有非晶涂层的硅晶圆上以及现有的 TMD 上生长了 TMD。为了鼓励原子将自己排列成高质量的单晶形式,而不是随机的多晶无序状态,Kim 和他的同事首先在硅片上覆盖了一层非常薄的薄膜或二氧化硅“掩模”,并用它进行了图案化微小的开口或口袋。

然后,他们将原子气体流过掩模,发现原子作为“种子”落入口袋中。这些口袋限制了种子以规则的单晶图案生长。

但当时,这种方法只能在 900 摄氏度左右发挥作用。

“你必须在 400 摄氏度以下的温度下生长这种单晶材料,否则底层电路就会完全煮熟并被毁掉,”Kim 说。“所以,我们的作业是,我们必须在低于 400 摄氏度的温度下进行类似的技术。如果我们能做到这一点,影响将是巨大的。”

建立

在他们的新工作中,Kim 和他的同事希望微调他们的方法,以便在足够低的温度下生长单晶二维材料,以保护任何底层电路。他们在冶金学——金属生产的科学和工艺——中找到了一个令人惊讶的简单解决方案。

当冶金学家将熔融金属倒入模具中时,液体会慢慢“成核”,或形成晶粒,这些晶粒长大并合并成规则图案的晶体,然后硬化成固体形式。冶金学家发现,这种成核最容易发生在注入液态金属的模具的边缘处。

“众所周知,边缘成核需要较少的能量和热量,”金说。“所以我们借用了冶金学的这个概念来用于未来的人工智能硬件。”

该团队希望在已经用晶体管电路制造的硅晶圆上生长单晶 TMD。该团队首先用二氧化硅掩模覆盖电路,就像他们之前的工作一样。

然后,他们将 TMD“种子”沉积在口罩每个口袋的边缘,发现这些边缘种子在低至 380 摄氏度的温度下生长成单晶材料,而与在中心开始生长的种子相比,远离从每个口袋的边缘开始,这需要更高的温度才能形成单晶材料。

更进一步,研究人员使用新方法制造了一种多层芯片,该芯片具有两种不同 TMD 的交替层——二硫化钼,一种用于制造 n 型晶体管的有前途的候选材料;以及二硒化钨,一种有潜力制成 p 型晶体管的材料。

p 型和 n 型晶体管都是执行任何逻辑运算的电子构建块。该团队能够以单晶形式直接在彼此之上生长两种材料,而不需要任何中间硅片。

Kim 表示,该方法将有效地将芯片半导体元件的密度增加一倍,特别是金属氧化物半导体(CMOS),它是现代逻辑电路的基本构建模块。

“通过我们的技术实现的产品不仅是 3D 逻辑芯片,而且是 3D 存储器及其组合,”Kim 说。“通过我们基于增长的单片 3D 方法,您可以在彼此之上生长数十到数百个逻辑和存储层,并且它们将能够很好地通信。”

“传统的 3D 芯片是用硅第一作者 Kiseok Kim 补充道:“通过在晶圆上钻孔,这种工艺限制了堆叠层数、垂直对准分辨率和良率。我们基于生长的方法可以同时解决所有这些问题”。

为了进一步将其可堆叠芯片设计商业化,Kim 最近成立了一家公司 FS2(未来半导体 2D 材料)。

“到目前为止,我们展示了小型设备阵列的概念,”他说。“下一步是扩大规模,展示专业的AI芯片运作。”

更多信息:Jeehwan Kim,基于生长的单晶 2D 半导体单片 3D 集成,自然(2024)。DOI:10.1038/s41586-024-08236-9。www.nature.com/articles/s41586-024-08236-9这个故事由麻省理工学院新闻转载(

web.mit.edu/新闻办公室/),一个热门网站,涵盖有关麻省理工学院研究、创新和教学的新闻。引文

:工程师开发“高层”3D 芯片,实现更高效的 AI 硬件(2024 年 12 月 18 日)检索日期:2024 年 12 月 18 日来自 https://techxplore.com/news/2024-12-high-3d-chips-enabling-efficient.html

本文档受版权保护。除了出于私人学习或研究目的的任何公平交易外,不得未经书面许可,不得复制部分内容。所提供的内容仅供参考。