华为拥有提交了专利对于四芯片设计,可用于其下一代AI加速器,即Ascend 910d。华为的Quad-Chiplet设计无疑模仿了NVIDIA的四芯片鲁宾Ultra的方法,但是围绕华为对其先进芯片包装的计划的专利,还有一件有趣的事情 - Huawei似乎正在开发具有与TSMC TSMC高级TSMC的先进包装技术相媲美的技术。最终,这可以使公司能够避开美国的制裁,并更快地赶上NVIDIA的AI GPU表现。

当然,该细节是在描述如何制作四芯片处理器的专利中。虽然我们不能确定它是上升的910d,但我们当然可以连接一些点并对可能的部分进行假设(尽管专利当然也不表明这一点)。它还与当前的芯片行业内部人士聊天一致,这表明正在制作四芯片910D。

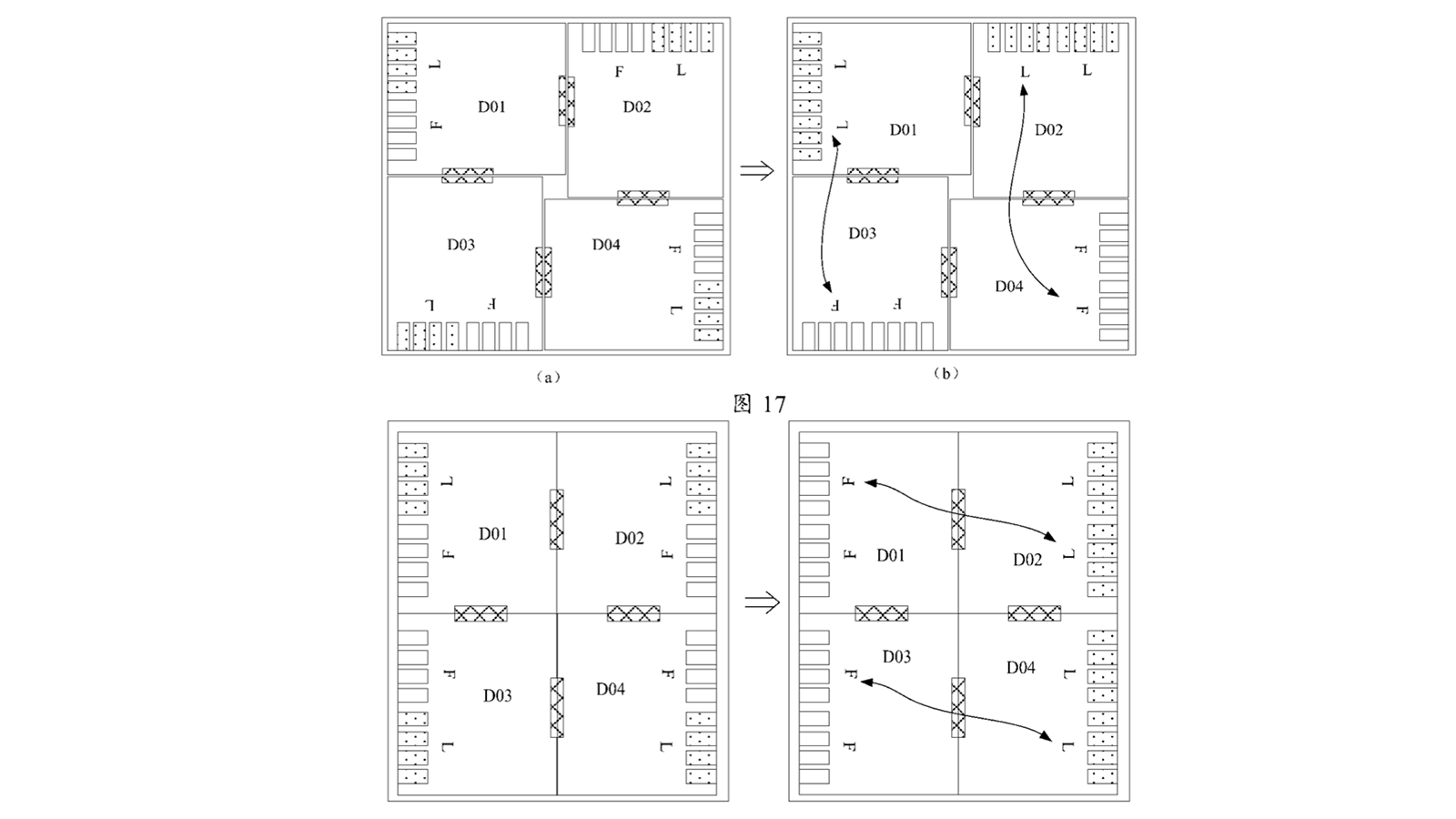

关于传闻上的Ascend 910d的一个更有趣的部分是计算芯片之间的互连,它们看起来像桥梁(TSMC的cowos-l或Intel的EMIB与Foveros 3D),而不是仅仅是插头(至少是从专利的角度来看)。同时,设计用于AI培训的处理器应伴随一堆HBM级内存模块,这些模块可能使用室间级互连。

尽管Smic和华为在光刻方面肯定是落后的,但在包装方面,它们可能与TSMC相提并论。这将是一个关键的发展,它将帮助中国避开美国出口限制的影响,从而阻止使用领先的芯片制造业。取而代之的是,中国公司可以简单地使用高级包装使用较旧的流程节点技术将多个芯片结合在一起,从而使它们能够匹配或至少接近使用前沿过程节点制造的芯片的性能。

这是我们无法确认的一些困难数学:单芯片上升的910b被认为具有665 mmm的死亡尺寸,因此在910d的情况下,我们可以将其四倍地达到2,660mmâ²(尽管请务必牢记)。由于每910B都带有四个HBM芯片(让我们假设它们是85mmâ²),其中四个将使HBM内存堆栈计数增加到16,从而使Dram的足迹达到了1,366 mm的高度。

这使我们进入投机性领土,但生产一个上升的910D处理器将至少需要总硅面积为4,020 mmm -²。按照TSMC的标准,这是五个EUV标线尺寸(858mmâ²),这是该公司计划在2026年引入数量生产的一种包装。

当我们第一次听到有关华为的四芯片上升910D加速器的谣言,该加速器于4月回到了AI时,我们当时拿着一勺盐和一小撮胡椒粉将其带回来。但是,谣言现在正在引起关注,华为确实正在为一个名为Ascend 910d的四型处理器工作,该处理器预计将超过NVIDIA的H100,在人均包装性能中。我们仍然应该用一粒盐(至少不是一块盐)将其服用,因为并非所有专利申请最终都会导致实际产品。

除了910d,华为是据报道工作在第920名绰号的未来处理器上,但该部分应该与Nvidia的H20竞争。当然,这个命名计划是不合逻辑的,但是由于该报告背后可能有一些优点,因此我们也应该记住这一点。

跟随汤姆在Google新闻上的硬件在您的提要中获取我们的最新新闻,分析和评论。确保单击“关注”按钮。