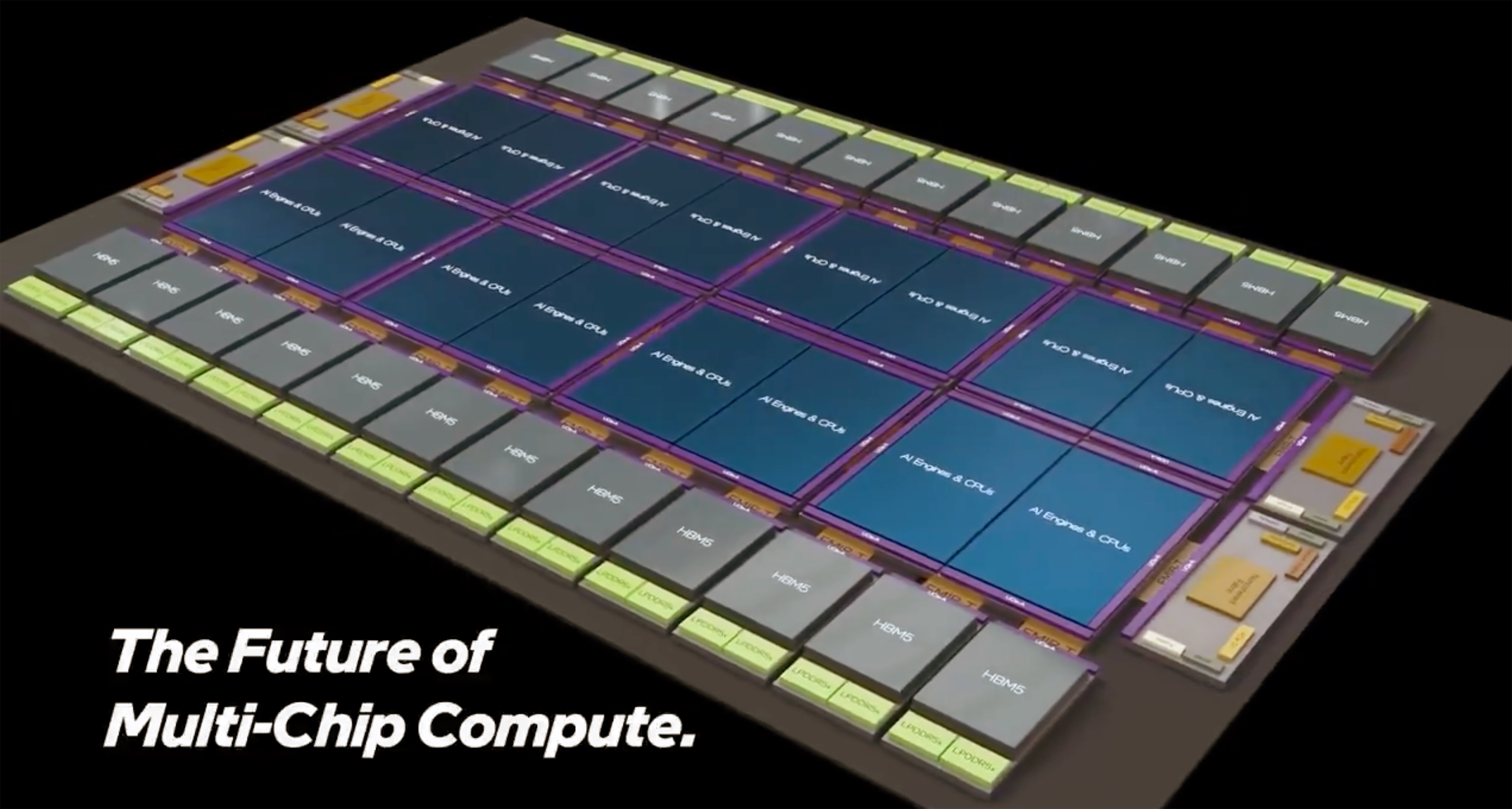

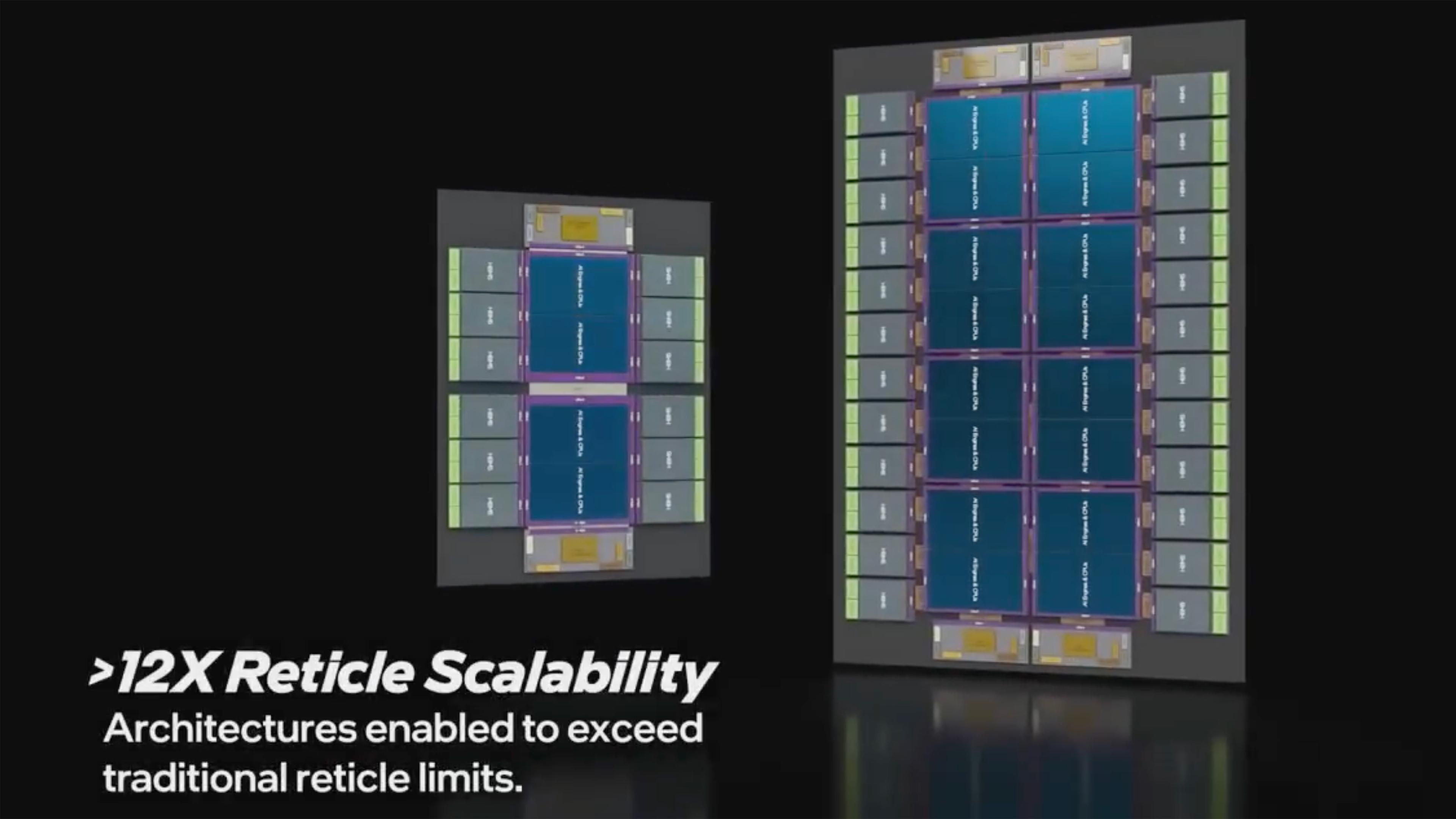

英特尔是第一家构建明确分解的小芯片设计的公司,该设计由 47 个小芯片组成,其 Ponte Vecchio 计算 GPU 用于 AI 和 HPC 应用。该产品仍然保持着最多人使用的多层瓷砖设计的记录,但是英特尔代工厂设想了更加极端的东西:多芯片封装,跨 8 个基础芯片集成至少 16 个计算元件、24 个 HBM5 内存堆栈,并可扩展至市场上最大 AI 芯片尺寸的 12 倍(12 倍标线尺寸,击败台积电的 9.5x 十字线尺寸)。当然,我们只能想知道这种野兽处理器的功耗和冷却要求。

它们位于 8 个(大概是十字线大小的)计算基础芯片之上,这些芯片由 18A-PT(1.8nm 级、通过硅通孔 (TSV) 和背面供电增强性能)制成,可以执行一些额外的计算工作,或者为“主”计算芯片提供大量 SRAM 缓存,如英特尔在其示例中所示。

从尖端互连到系统级组装和测试,英特尔代工厂提供了为下一代多芯片平台提供动力所需的规模和集成。https://t.co/smSje92QQh #IntelFoundry #Semiconductors pic.twitter.com/4sAVftVRhg2025 年 12 月 22 日

*展开上面的推文即可观看飞行视频。

基础芯片使用以下方式连接到计算块Foveros 直接 3D,利用超高密度亚 10 µm 铜对铜混合键合,为顶部芯片提供最大带宽和功率。英特尔的 Foveros Direct 3D 目前是英特尔代工封装创新的巅峰之作,凸显了非常复杂的设计。

基础芯片利用 EMIB-T(带有 TSV 的嵌入式多芯片互连桥的增强版本),UCle-A在顶部,用于它们之间的横向(2.5D)互连以及与 18A-P(1.8nm 级,性能增强)上制造的 I/O 芯片以及定制基础芯片的互连,最多可容纳 24 个 HBM5 内存堆栈。

Tom 的硬件高级路线图

值得注意的是,英特尔建议使用EMIB-T和顶部的UCIe-A来连接定制的HBM5模块,而不是使用具有行业标准接口的JEDEC标准HBM5堆栈,可能是为了获得更多的性能和容量。鉴于演示的概念性质,使用定制 HBM5 堆栈并不是设计要求;这只是表明英特尔也集成此类设备的一种方式。

整个套件还可以搭载 PCIe 7.0、光学引擎、非相干结构、224G SerDes、专有加速器等安全,甚至还可以使用 LPDDR5X 内存来增加 DRAM 容量。

请注意,Intel Foundry 在 X 上发布的视频显示了两种概念设计:一种是“中型”设计,具有 4 个计算块和 12 个 HBM,另一种是“极端”设计,具有 16 个计算块和 24 个 HBM5 堆栈,这也是我们故事的重点。以今天的标准来看,即使是中型设计也相当先进,但英特尔现在就可以生产它。

至于极端概念,可能会在本世纪末出现,届时英特尔不仅完善了 Foveros Direct 3D 封装技术,还完善了其 18A 和 14A 生产节点。能够在本世纪末生产如此极端的封装将使英特尔与台积电相媲美,台积电也有类似的计划,甚至预计至少有一些客户将在 2027 年至 2028 年左右使用其晶圆尺寸集成产品。

在短短几年内将极限设计变为现实对英特尔来说是一项重大挑战,因为它必须确保组件在连接到主板时不会变形,并且即使在最小公差的情况下也不会因长时间使用后过热而变形。除此之外,英特尔(以及整个行业)将需要学习如何为智能手机尺寸(最大 10,296 mm^2)的巨大处理器设计提供支持和冷却,该处理器将具有更大的封装,但这是一个不同的故事。

关注Google 新闻上的 Tom's Hardware, 或将我们添加为首选来源,在您的源中获取我们的最新新闻、分析和评论。