超 ethernet consoritum(UEC)将规格版本 1.0 的发布从 2024 年第三季度推迟到 2025 年第一季度,但看起来像AMD准备宣布一款专为人工智能数据中心设计的实际网络接口卡,可部署到超以太网数据中心。新的单元是AMD Pensando Pollara 400,它承诺可以将AI工作负载的性能提高多达六倍。

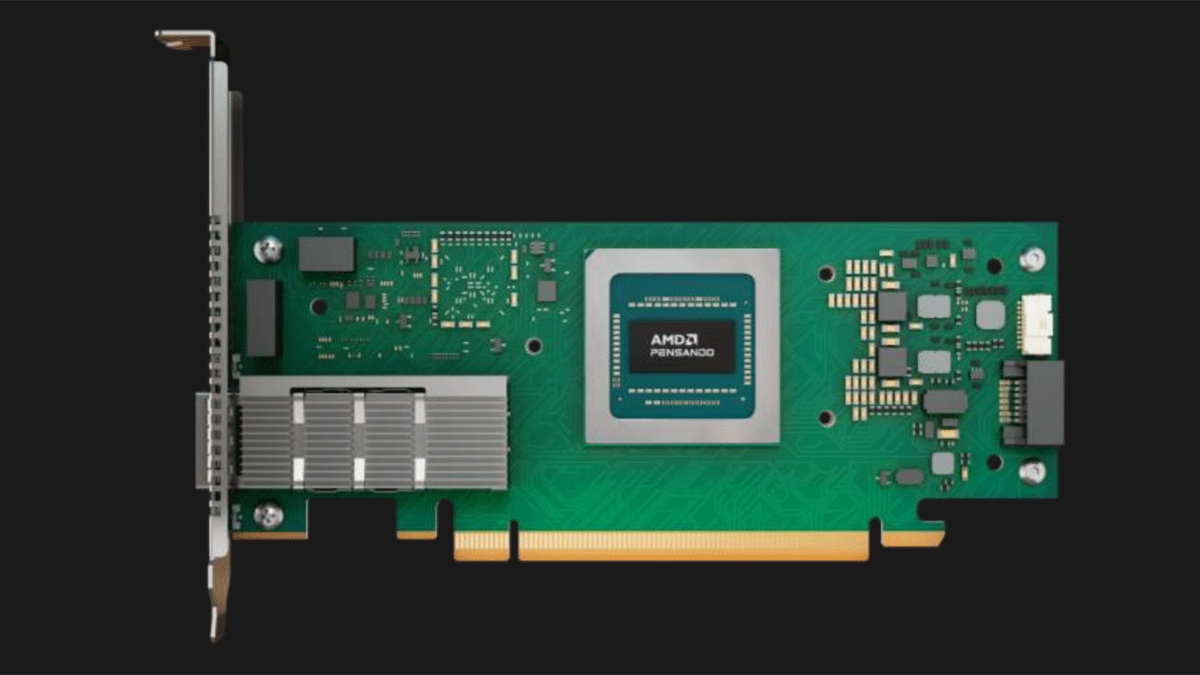

AMD Pensando Pollara 400 是一款基于该公司 Pensando 部门设计的处理器的 400 GbE 超级以太网卡。该网络处理器具有可编程硬件流水线、可编程 RDMA 传输、可编程拥塞控制和通信库加速功能。该 NIC 将在第四季度进行采样,并将于 2025 年上半年正式上市,紧随超级以太网联盟正式发布 UEC 1.0 规范之后。

AMD Pensando Pollara 400 AI网卡设计通过多种高级功能优化AI和HPC网络。其关键特性之一是智能多路径技术,该技术能够动态地将数据包分布在最优路由上,防止网络拥塞并提高整体效率。此外,该网卡还包含路径感知的拥塞控制功能,可以将数据从暂时拥塞的路径重新定向到其他路径,以确保持续的高速数据流。

此外,Pollara 400 提供快速故障切换功能,能够迅速检测并绕过网络故障,以保持不间断的 GPU 到 GPU 的通信,从而在最大化利用 AI 集群的同时提供强大的性能并最小化延迟。这些特性承诺增强 AI 基础设施的可扩展性和可靠性,使其适合大规模部署。

超以太网联盟目前包括97名成员,而这一数字在2024年3月时为55名。UEC 1.0规范旨在根据性能和功能扩展通用的以太网技术,以适应AI和HPC工作负载的需求。新的规范将尽可能多地利用原有技术,以保持成本效益和互操作性。该规范将针对AI和HPC制定不同的配置文件;尽管这些工作负载有很多共同之处,但它们在许多方面都有显著差异,因此为了最大化效率,将会有单独的协议。